# Alpha Bridge AQSDH-T-1-PCV Datasheet

#### Features

- Up to 800Gb/s data rate

- 8x100Gb/s PAM4 modulation

- Compatible to QSFP-DD Hardware Specification

- Compatible to IEEE802.3cK

- Hot-pluggable

- Power Supply Voltage: 3.3W

- RoHS compliant

- Operating temperature range: 0°C to 70°C

#### Application

- Switches, Servers, RouterS, Storage Arrays

- Networking Equipment

- Data Cables

- Telecommunications Central Offices

- Test and Measurement Equipment

- Test and Measurement Equipment

#### Description

AlphaBridge QSFP-DD800 (Double Density) Passive Direct Attach Copper Cable features 8 transmitting and 8 receiving 100Gbps PAM4 channels for 800G operation. The cable assembly meets IEEE 802.3ck 400GBase -CR4, 200Gbase-CR2 and 100GBase-CR1 standards with substantial signal integrity margin providing high performance and bandwidth interconnect solutions for high-density applications.

As next-gen data centres deploy faster speed in a tighter space, they need high performance cables that reduce power consumption, provide reliable operation and are low cost. AlphaBridge QSFP-DD800 cable is designed to meet the next-gen data centre needs. With unique foam dielectric construction, Volex QSFP-DD800 cable offers smallestcable outer diameter and bend radius, and highest flexibility, while meeting or exceeding the MSA signal integrity specification.

#### Absolute Maximum Ratings

| Parameter                            | Symbol | Min.  | Тур. | Max.  | Units |

|--------------------------------------|--------|-------|------|-------|-------|

| Storage Temperature                  | TS     | -40   |      | 85    | °C    |

| Supply Voltage                       | VCC3   | 3.135 |      | 3.465 | V     |

| Relative Humidity (non-condensation) | RS     | 5     |      | 85    | %     |

| Recommended Operating Conditions & Power Supply Requirements |         |       |  |           |    |  |  |

|--------------------------------------------------------------|---------|-------|--|-----------|----|--|--|

| Parameter                                                    | Мах.    | Units |  |           |    |  |  |

| Operating Case Temperature                                   | ТОР     | 0     |  | 70        | °C |  |  |

| Power Supply Voltage                                         | VCC3    | 3.135 |  | 3.465     | V  |  |  |

| Voltage on LVTTL Input                                       | Vilvttl | -0.3  |  | VCC3 +0.2 | V  |  |  |

| Power Supply Current                                         | lcc3    | 0.001 |  |           | mA |  |  |

# Frequency Domain

| Item | Test Parameter                         | IEEE802.3ck Specification                                        |  |  |

|------|----------------------------------------|------------------------------------------------------------------|--|--|

|      |                                        | Maximum insertion loss at 26.56GHz -17.16dB                      |  |  |

| 1    | Differential Insertion Loss (SDD21)    | Minimum insertion loss at 26.56GHz -8dB                          |  |  |

| -    |                                        | -1.4dB @ 0.05 to 6GHz                                            |  |  |

| 2    | Common Mode Reflection (SCC11/SCC22)   | -0.68-0.12*(f) @ 6 to 30GHz                                      |  |  |

|      |                                        | -10.28+0.2*(f) @ 30 to 40GHz                                     |  |  |

|      | Common Mode Conversion                 | -22+(10/25.56)*(f) @ 0.05 to 26.56GHz                            |  |  |

| 3    | (SCD11/SCD22)                          | -15+(3/25.56)*(f) @ 26.56 to 40GHz                               |  |  |

|      | Differential to Common Mode Conversion | -10dB @ 0.05 to 12.89GHz                                         |  |  |

| 4    | Loss (SCD21-SDD21)                     | -14+0.3108*(f) @ 12.89 to 40GHz                                  |  |  |

| 5    | Channel Operating Margin (COM)         | 3dB Minimum                                                      |  |  |

|      |                                        | * 8.25 dB Minimum.                                               |  |  |

| 6    | Effective Return Loss (ERL)            | Cable assemblies with a COM greater than 4 dB are notrequired to |  |  |

|      |                                        | meet minimum ERL                                                 |  |  |

| 7    | Insertion Loss* (SDD21) for 0.5M 30awg | 25.65GHz : -14.55 dB Max                                         |  |  |

|      | Insertion Loss* (SDD21) for 1.0M 28awg | 25.65GHz : -16.75 dB Max                                         |  |  |

|      | Insertion Loss* (SDD21) for 1.5M 26awg | 25.65GHz : -17.45 dB Max                                         |  |  |

|      | Insertion Loss* (SDD21) for 2.0M 26awg | 25.65GHz : -19.75 dB Max                                         |  |  |

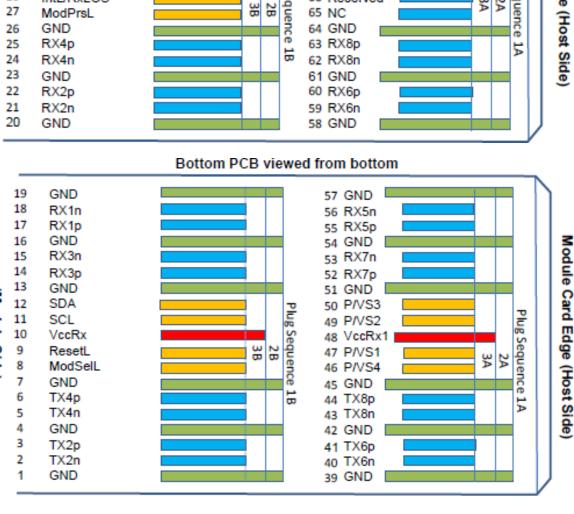

# Pin Description

| Pin | Logic   | Symbol  | Description                        | Notes |

|-----|---------|---------|------------------------------------|-------|

| 1   |         | GND     | Ground                             | 1     |

| 2   | CML-I   | Tx2n    | Transmitter Inverted Data Input    |       |

| 3   | CML-I   | Tx2p    | Transmitter Non-Inverted DataInput |       |

| 4   |         | GND     | Ground                             | 1     |

| 5   | CML-I   | Tx4n    | Transmitter Inverted Data Input    |       |

| 6   | CML-I   | Tx4p    | Transmitter Non-Inverted DataInput |       |

| 7   |         | GND     | Ground                             | 1     |

| 8   | LVTTL-I | ModSeIL | Module Select                      |       |

|    | LVTTL-I    | ResetL  | Module Reset                          |

|----|------------|---------|---------------------------------------|

|    |            | Vcc Rx  | +3.3V Power Supply Receiver           |

| L  | .vcmosi/o  | SCL     | 2-wire serial interface clock 2       |

| L  | .vcmosi/o  | SDA     | 2-wire serial interface data 2        |

|    |            | GND     | Ground 1                              |

|    | CML-0      | Rx3p    | Receiver Non-Inverted Data Output     |

|    | CML-0      | Rx3n    | Receiver Inverted Data Output         |

|    |            | GND     | Ground 1                              |

|    | CML-0      | Rx1p    | Receiver Non-Inverted Data Output     |

|    | CML-0      | Rx1n    | Receiver Inverted Data Output         |

|    |            | GND     | Ground 1                              |

|    |            | GND     | Ground 1                              |

|    | CML-0      | Rx2n    | Receiver Inverted Data Output         |

|    | CML-0      | Rx2p    | Receiver Non-Inverted Data Output     |

|    |            | GND     | Ground 1                              |

|    | CML-0      | Rx4n    | Receiver Inverted Data Output         |

|    | CML-0      | Rx4p    | Receiver Non-Inverted Data Output     |

|    |            | GND     | Ground 1                              |

|    | LVTTL-0    | ModPrsL | Module Present 2                      |

|    | LVTTL-0    | IntL    | Interrupt 2                           |

|    |            | Vcc Tx  | +3.3V Power Supply transmitter        |

|    |            | Vcc1    | +3.3V Power Supply                    |

|    | LVTTL-I    | LPMode  | Low Power Mode                        |

|    |            | GND     | Ground 1                              |

|    | CML-I      | Тх3р    | Transmitter Non-Inverted Data Input   |

|    | CML-I      | Tx3n    | Transmitter Inverted Data Input       |

|    |            | GND     | Ground 1                              |

|    | CML-I      | Tx1p    | Transmitter Non-Inverted Data Input   |

|    | CML-I      | Tx1n    | Transmitter Inverted Data Input       |

|    |            | GND     | Ground 1                              |

|    |            | GND     | Ground                                |

|    | CML-I      | Tx6n    | Transmitter Inverted Data Input       |

|    | CML-I      | Тх6р    | Transmitter Non-Inverted Data output  |

|    |            | GND     | Ground                                |

|    | CML-I      | Tx8n    | Transmitter Inverted Data Input       |

|    | CML-I      | Тх8р    | Transmitter Non-Inverted Data output  |

|    |            | GND     | Ground                                |

| LV | CMOS/CML-I | P/VS4   | Programmable/Module Vendor Specific 4 |

|    | CMOS/CML-I | P/VS1   | Programmable/Module Vendor Specific 1 |

| 48 |              | VccRx1     | + 3.3V Power Supply                     |  |

|----|--------------|------------|-----------------------------------------|--|

| 49 | LVCMOS/CML-O | P/VS2      | Programmable/Module Vendor Specific 2   |  |

| 50 | LVCMOS/CML-O | P/VS3      | Programmable/Module Vendor Specific 3   |  |

| 51 |              | GND        | Ground                                  |  |

| 52 | CML-0        | Rx7p       | Receiver Non-Inverted Data Output       |  |

| 53 | CML-O        | Rx7n       | Receiver Inverted Data Output           |  |

| 54 |              | GND        | Ground                                  |  |

| 55 | CML-O        | Rx5p       | Receiver Non-Inverted Data Output       |  |

| 56 | CML-0        | Rx5n       | Receiver Inverted Data Output           |  |

| 57 |              | GND        | Ground                                  |  |

| 58 |              | GND        | Ground                                  |  |

| 59 | CML-O        | Rx6n       | Receiver Inverted Data Output           |  |

| 60 | CML-O        | Rx6p       | Receiver Non-Inverted Data Output       |  |

| 61 |              | GND        | Ground                                  |  |

| 62 | CML-O        | Rx8n       | Receiver Inverted Data Output           |  |

| 63 | CML-O        | Rx8p       | Receiver Non-Inverted Data Output       |  |

| 64 |              | GND        | Ground                                  |  |

| 65 |              | NC         | No Connect                              |  |

| 66 |              | Reserved   | For future use                          |  |

| 67 |              | VccTx      | +3.3 V Power Supply                     |  |

| 68 |              | Vcc2       | +3.3 V Power Supply                     |  |

| 69 | LVCMOS-I     | ePPS/Clock | 1PPS PTP clock or reference clock input |  |

| 70 |              | GND        | Ground                                  |  |

| 71 | CML-I        | Tx7p       | Transmitter Non-Inverted Data Input     |  |

| 72 | CML-I        | Tx7n       | Transmitter Inverted Data Output        |  |

| 73 |              | GND        | Ground                                  |  |

| 74 | CML-I        | Tx5p       | Transmitter Non-Inverted Data Input     |  |

| 75 | CML-I        | Tx5n       | Transmitter Inverted Data Output        |  |

| 76 |              | GND        | Ground                                  |  |

Note:

- QSFP-DD 800G uses common ground (GND) for all signals and supply (power). All are common within the QSFP-DD 800G module and all module voltages are referenced to this potential unless otherwise noted. Connect these directly to the host board signal-common ground plane. Each connector Gnd contact is ratedfor a maximum current of 500 mA.

- 2. VccRx, VccRx1, Vcc1, Vcc2, VccTx and VccTx1 shall be applied concurrently. Supply requirements defined for the host side of the Host Card Edge Connector are listed in Table 10. For power classes 4 and above themodule differential loading of input voltage pads must not result in exceeding contact current limits. Each connector Vcc contact is rated for a maximum current of 1500 mA.

- Reserved and no Connect pads recommended to be terminated with 10 k to ground on the host. Pad 65 (No Connect) shall be left unconnected within the module.

- 4. Plug Sequence specifies the mating sequence of the host connector and module. The sequence is 1A, 2A, 3A, 1B, 2B, 3B. (see Figure 2 for pad locations) Contact sequence A will make, then break contact with additional QSFP-DD 800G pads. Sequence 1A and 1B will then occur simultaneously, followed by 2A and 2B, followed by 3A and 3B.

- Full definitions of the P/VSx signals currently under development. On new designs not used P/VSx signals are 5. recommended to be terminated on the host with 10 k $\Omega$ .

- ePPS/Clock if not used recommended to be terminated with  $50\Omega$  to ground on the host 6.

#### 38 GND 76 GND 37 TX1n 75 TX5n 36 TX1p 74 TX5p 35 GND 73 GND Module Card Edge (Host Side) 34 TX3n 72 TX7n 33 TX3p 71 TX7p 32 70 GND GND (Module Side) 31 LPMode/TxDis 69 ePPS/Clock Plug Sequence Plug 68 Vcc2 30 Vcc1 29 VccTx 67 VccTx1 Sequence 28 IntL/RxLOS 66 Reserved ¥ Ϋ́ œ 28 27 ModPrsL 65 NC 26 GND 64 GND RX4p 25 63 RX8p 5 н 24 RX4n 62 RX8n 23 GND 61 GND 22 RX2p 60 RX6p 21 RX2n 59 RX6n 20 GND 58 GND Bottom PCB viewed from bottom 19 GND 57 GND 18 RX1n 56 RX5n 17 RX1p 55 RX5p 16 GND GND 54 15 RX3n 53 RX7n 14 RX3p 52 RX7p 13 GND GND 51 (Module Side) 12 SDA P/VS3 50 11 SCL

#### **Pin Assignment**

#### Top PCB viewed from top

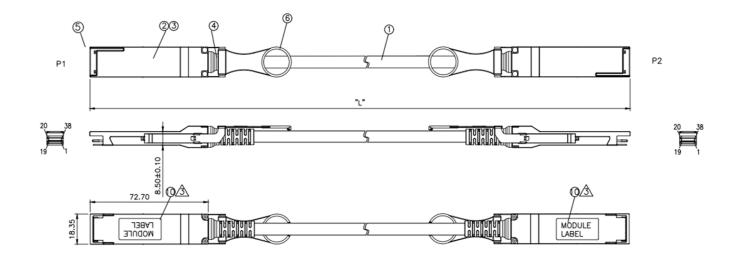

#### Dimensions

### Ordering Information

| Model Number       | Part Number   | AWG | Length | Temperature                           |

|--------------------|---------------|-----|--------|---------------------------------------|

| 800G QSF-DD DAC-1M | AQSDH-T-1-PCV | 28  | 1M     | 0 <sup>°</sup> C to 70 <sup>°</sup> C |

Note: All information contained in this document is subject to change without notice.

Copyright @ Alpha Bridge Technologies Private Limited

This document is ABTPL Public Information. ABTPL reserves the right to alter, update and otherwise change the information contained in the document from time to time. www.alphabridge.tech