Alpha Bridge AQSFP-DD-DR4+ Datasheet

#### **Features**

- QSFP-DD MSA-compliant

- Parallel 4 Optical Lanes

- 100G Lambda MSA 100G-FR Specification compliant

- Up to 2km transmission on single mode fiber (SMF) with FEC

- 8x53.125Gb/s electrical interface (400GAUI-8)

- Data Rate 106.25Gbps (PAM4) per channel

- Maximum power consumption 8.5W

- MPO-12 connector

- Operating case temperature: 0°C ~70°C

- RoHS compliant

#### **Applications**

- 400G Ethernet

- Infini interconnects

- Datacenter Enterprise networking

### **Description**

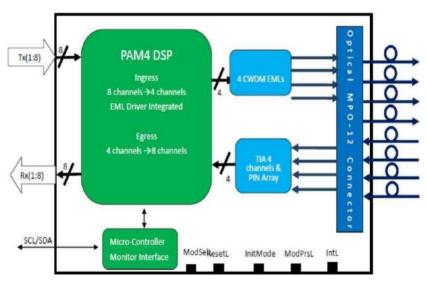

This product is a 400Gb/s Quad Small Form Factor Pluggable-double density (QSFP-DD) optical module designed for 2km optical communication applications. The module converts 8 channels of 50Gb/s (PAM4) electrical input data to 4 channels of parallel optical signals, each capable of 100Gb/s operation for an aggregate data rate of 400Gb/s. Reversely, on the receiver side, the module converts 4 channels of parallel optical signals of 100Gb/s each channel for an aggregate data rage of 400Gb/s into 8 channels of 50Gb/s (PAM4) electrical output data.

An optical fiber cable with an MTP/MPO-12 connector can be plugged into the QSFP-DD DR4 module receptacle. Proper alignment is ensured by the guide pins inside the receptacle. The cable usually cannot be twistedfor proper channel to channel alignment. Electrical connection is achieved through a QSFP-DD MSA-compliant edgetype connector.

The product is designed with form factor, optical/electrical connection and digital diagnostic interface according to the QSFP-DD Mulit-Source Agreement (MSA) Type 2. It has been designed to meet the harshest external operating conditions including temperature, humidity and EMI interference.

**Absolute Maximum Ratings**

| Parameter                   | Symbol | Min. | Мах. | Units | Note |

|-----------------------------|--------|------|------|-------|------|

| Storage Temperature         | Tst    | -40  | 85   | °C    |      |

| Supply Voltage              | Vcc    | -0.5 | 3.6  | V     |      |

| Case Operating Temperature  | Тор    | 0    | 70   | °C    |      |

| Humidity (non-condensing)   | Rh     | 0    | 85   | %     |      |

| Damage Threshold, each Lane | THd    | 5    |      | dBm   |      |

**Recommended Operating Conditions**

| Parameter                       | Symbol | Min.  | Тур.    | Мах.    | Units |

|---------------------------------|--------|-------|---------|---------|-------|

| Operating Case Temperature      | Тса    | 0     |         | 70      | °C    |

| Supply Voltage                  | Vcc    | 3.135 | 3.3     | 3.465   | V     |

| Electrical Data Rage, each Lane |        |       | 26.5625 |         | GBd   |

| Optical Data Rage, each Lane    |        |       | 53.125  |         | GBd   |

| Power Supply Noise              | Vn     |       |         | 66      | mV    |

| Data Rate Accuracy              |        | -100  |         | 100     | ppm   |

| Pre-FEC Bit Error Ratio         |        |       |         | 24x10-4 |       |

| Post-FEC Bit Error Ratio        |        |       |         | 1x10-15 |       |

| Control Input Voltage High      |        | 2     |         | Vcc     | V     |

| Control Input Voltage Low       |        | 0     |         | 0.8     | V     |

| Link Distance                   | D      | 0.002 |         | 2       |       |

Notes:

- 1. FEC provided by host system.

- 2. FEC required on host system to support maximum distance.

**Diagnostic Monitoring Interface**

| Parameter                             | Symbol          | Accuracy | Unit | Notes           | Parameter              |

|---------------------------------------|-----------------|----------|------|-----------------|------------------------|

| Temperature monitor absolute error    | DMI_Temp        | ± 3      | °C   | Over operating  | Temperature monitor    |

| remperature moment absolute error     | Divii_Temp      |          |      | over operating  | absolute error         |

| Supply voltage monitor absolute error | DMI_VCC         | ± 0.1    | V    | Over full       | Supply voltage monitor |

| Supply voltage monitor absolute error | Divii_vcc       | 10.1     | V    | operating range | absolute error         |

| Channel RX power monitor absolute     | DMI RX Ch       | ± 3      | dB   | 1               | Channel RX power       |

| error                                 | DIVII_KX_CII    | ± 3      | uв   | 1               | monitor absolute error |

| Channel Bias current monitor          | DMI Ibias Ch    | ± 10%    | mA   |                 | Channel Bias current   |

| Chainlei bias current monitor         | Divii_ibias_Cii | 110/0    | IIIA |                 | monitor                |

| Channel TX power monitor absolute     | DMI_TX_Ch       | ± 3      | dB   | 1               | Channel TX power       |

| error                                 | DIVII_1X_CII    | <u> </u> | uD   | l l             | monitor absolute error |

#### Notes:

1.Due to the measurement accuracy of different single-mode fibers, there could be an additional +/-1 dB fluctuation or a

+/-3 dB total accuracy.

**Optical Characteristics**

| Parameter                                                               | Symbol           | Min.     | Тур.     | Max.   | Units | Note       |  |  |  |

|-------------------------------------------------------------------------|------------------|----------|----------|--------|-------|------------|--|--|--|

| Signaling Rate, each Lane                                               | DR               |          | 53.125 ± | 100ppm | GBd   | PAM4       |  |  |  |

| Center Wavelength                                                       | λс               | 1304.5   | 1310     | 1317.5 | NM    |            |  |  |  |

|                                                                         |                  | Transmit | ter      |        |       |            |  |  |  |

| Side-mode Suppression Ratio                                             | SMSR             | 30       |          |        | dB    |            |  |  |  |

| Average Launch Power, each Lane                                         | P <sub>AVG</sub> | -2.4     |          | 4      | dBm   | 1          |  |  |  |

| Optical Modulation Amplitude                                            | Рома             | -0.2     |          | 4.2    |       |            |  |  |  |

| (OMA <sub>outer</sub> ), each Lane                                      |                  |          |          |        | dBm   | 2          |  |  |  |

| Launch Power in OMA <sub>outer</sub> minus                              |                  | -1.6     |          |        | dB    | For ER≧5dB |  |  |  |

| TDECQ, each Lane                                                        |                  | -1.5     |          |        | dB    | For ER≦5dB |  |  |  |

| Transmitter and Dispersion Eye<br>Closure for PAM4(TDECQ), each<br>lane | TDECQ            |          |          | 3.4    | dB    | SSPRQ      |  |  |  |

| TDECQ-10*log <sub>10</sub> (C <sub>eq</sub> ) ,each Lane                |                  |          |          | 3.4    | dB    | 3          |  |  |  |

| Extinction Ratio                                                        | ER               | 3.5      |          |        | dB    |            |  |  |  |

| RIN <sub>21.4</sub> OMA                                                 | RIN              |          |          | -136   | dB/Hz |            |  |  |  |

| Optical Return Loss Tolerance                                           | TOL              |          |          | 17.1   | dB    |            |  |  |  |

| Transmitter Reflectance                                                 | Rt               |          |          | -26    | dB    |            |  |  |  |

| Average Launch Power of OFF                                             |                  |          |          |        |       |            |  |  |  |

| Transmitter, each Lane                                                  | Poff             |          |          | -15    | dBm   |            |  |  |  |

| LOS Assert Level                                                        | LOSA             |          | 50       |        | mV    | 4          |  |  |  |

| LOA De-assert Level                                                     | LOSD             |          | 100      |        | mV    |            |  |  |  |

|                                                                         | Receiver         |          |          |        |       |            |  |  |  |

| Damage Threshold, each Lane                                             | THd              | 5        |          |        | dBm   | 5          |  |  |  |

| Average receiver Power, each Lane                                       |                  | -6.4     |          | 4      | dBm   | 6          |  |  |  |

| Receiver Power (OMA <sub>outer</sub> ), each Lane                       |                  |          |          | 4.2    | dBm   |            |  |  |  |

| Receiver Sensitivity (OMAouter), each                                   |                  |          | Equation |        |       |            |  |  |  |

## AQSFP-DD-DR4+ Datasheet

|                                  | T             |                     | 1 .             |                    | l   |    |

|----------------------------------|---------------|---------------------|-----------------|--------------------|-----|----|

| Lane                             | SEN           |                     | -1              |                    | dBm | 7  |

| Stressed Receiver Sensitivity in |               |                     |                 |                    |     |    |

| OMA                              |               |                     |                 |                    |     |    |

| outer, each Lane                 | SRS           |                     |                 | -2                 | dBm | 8  |

| BER @RxAOP= -2dBm                |               |                     |                 | 2x10 <sup>-6</sup> |     | 9  |

| BER @RxAOP= -0dBm                |               |                     |                 | 2x10 <sup>-6</sup> |     | 9  |

| BER @RxAOP= +2dBm                |               |                     |                 | 2x10 <sup>-6</sup> |     | 9  |

| BER @RxAOP= +4.5dBm              |               |                     |                 | 2x10 <sup>-5</sup> |     | 9  |

| Receiver Reflectance             | RR            |                     |                 | -26                | dB  |    |

| LOS Assert                       | LOSA          | -15                 |                 | -11                | dBm | 10 |

| LOS De-assert                    | LOSD          | -14                 |                 | -10                | dBm |    |

| LOS Hysteresis                   | LOSH          | 0.5                 |                 | 5                  |     |    |

|                                  | Stressed Cond | itions for Stress R | eceiver Sensiti | vity (Note 8)      |     |    |

| Stressed Eye Closure for PAM4    |               |                     |                 |                    |     |    |

| (SECQ), Lane under Test          |               |                     | 3.4             |                    | dB  |    |

| SECQ-10*log10(Ceq), Lane under   |               |                     |                 | 3.4                | dB  |    |

| Test                             |               |                     |                 | 5.4                | ub  |    |

| OMAouter of each Aggressor Lane  |               |                     | 4.2             |                    | dBm |    |

#### Notes:

- 1. Average launch power, each lane (min) is informative and not the principal indicator of signal strength. A transmitter with launch power below this value cannot be compliant, however, a value above this does not ensure compliant.

- 2. Even if the TDECQ < 1.4dB for an extinction ratio of ≥5dB or TDECQ < 1.1dB for an extinction ratio of < 5dB, the OMA<sub>outer</sub> (min) must exceed the minimum value specified here.

- 3. C<sub>eq</sub> is a coefficient defined in IEEE Std 802.3-2018 clause 121.8.5.3 which accounts for reference equalizer noise enhancement.

- 4. Average receiver power, each lane (min) is informative and not the principal indicator of signal strength. A received power below this value cannot be compliant; however, a value above this does not ensure compliance.

- 5. The receiver shall be able to tolerate, without damage, continuous exposure to a modulated optical input signalhaving this power level on one lane. The receiver does not have to operate correctly at this input power.

- 6. Receiver sensitivity (OMA<sub>outer</sub>), each lane (max) is informative and is defined for a transmitter with a value of SECQ up to 3.4dB. It should meet Equation (1), which is illustrated in Figure 4.

RS=max (-3.9, SECQ-5.3) dBm (1)

Where

RS is the receiver sensitivity

SECQ is the SECQ of the transmitter used to measure the receiver sensitivity.

- 7. Measured with conformance test signal at TP3 for the BER equal to 2.4x10<sup>-4</sup>

- 8. These test conditions are for measuring stressed receiver sensitivity. They are not characteristics of thereceiver.

#### **Electronical Characteristics**

| Parameter                                        | Symbol | Min.                               | Тур.              | Max. | Units | Note |  |  |  |

|--------------------------------------------------|--------|------------------------------------|-------------------|------|-------|------|--|--|--|

| Power Consumption                                |        |                                    |                   | 8.5  | W     |      |  |  |  |

| Supply Current                                   | Icc    |                                    |                   | 2.58 | Α     |      |  |  |  |

| Power Supply Ripple                              |        |                                    |                   | 15   | mv    |      |  |  |  |

| Transmitter (each Lane)                          |        |                                    |                   |      |       |      |  |  |  |

| Signaling Rate, each Lane                        | TP1    | 26.5625 ± 100                      | 26.5625 ± 100 ppm |      | GBd   |      |  |  |  |

| Differential pk-pk Input voltage<br>Tolerance    | TP1a   | 900                                | 900               |      | mVpp  | 1    |  |  |  |

| Differential Termination Mismatch                | TP1    |                                    |                   |      | %     |      |  |  |  |

| Differential Input Return Loss                   | TP1    | IEEE 802.3- 2015 Equation -(83E-5) |                   |      | Db    |      |  |  |  |

| Differential to Common Mode Input<br>Return Loss | TP1    | IEEE 802.3- 2015 Equation -(83E-6) |                   |      | Db    |      |  |  |  |

# AQSFP-DD-DR4+ Datasheet

| Module Stressed Input Test                    | TP1a | See IEEE 802.3bs 120E.3.4.1       |     |      |      | 2 |

|-----------------------------------------------|------|-----------------------------------|-----|------|------|---|

| Single-ended Voltage Tolerance Range (Min)    | TP1a | -0.4 to 3.3                       |     |      | V    |   |

| DC Common Mode Input Voltage                  | TP1  | -350                              |     | 2850 | mV   | 3 |

| Input AC Coupling Capacitor                   | TP1a |                                   | 0.1 |      | uF   |   |

|                                               | F    | Receiver (each Lane)              |     |      |      |   |

| Differential Peak to Peak output voltage      | TP4  |                                   |     | 900  | mVpp |   |

| AC Common Mode Output Voltage,<br>RMS         | TP4  |                                   |     | 17.5 | mV   |   |

| Differential Termination Mismatch             | TP4  |                                   |     | 10   | %    |   |

| Differential Output Return Loss               | TP4  | IEEE 802.3- 2015 Equation (83E-2) |     |      |      |   |

| Common to Differential Mode Conversion Return | TP4  | IEEE 802.3-2015 Equation (83E-3)  |     |      |      |   |

| Transition Time, 20% to 80%                   | TP4  | 9.5                               |     |      | Ps   |   |

| Near-end Eye Symmetry Mask Width (ESMW)       | TP4  | 0.265                             |     |      | UI   |   |

| Near-end Eye Height, Differential             | TP4  | 70                                |     |      | mV   |   |

| Far-end Eye Symmetry Mask Width (ESMW)        | TP4  | 0.2                               |     |      | UI   |   |

| Far-end Eye Height, Differential              | TP4  | 30                                |     |      | mV   |   |

| Far-end Pre-cursor ISI Ratio                  | TP4  | -4.5                              |     | 2.5  | %    |   |

| Common Mode Output Voltage (Vcm)              | TP4  | -350                              |     | 2850 | mV   | 3 |

| Output AC Coupling Capacitor                  | TP4  |                                   | 0.1 |      |      |   |

**Block Diagram of Transceiver**

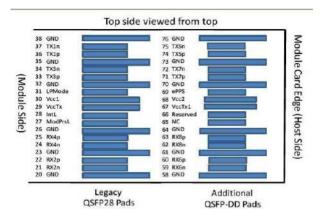

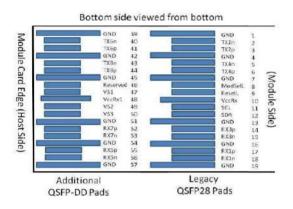

## **Pin Assignment and Description**

| PIN | Logic      | Symbol  | Name / Description                  | Note |

|-----|------------|---------|-------------------------------------|------|

| 1   |            | GND     | Ground                              |      |

| 2   | CML-I      | Tx2n    | Transmitter inverted data input     |      |

| 3   | CML-I      | Tx2p    | Transmitter non-inverted data input |      |

| 4   |            | GND     | Ground                              |      |

| 5   | CML-I      | Tx4n    | Transmitter inverted data input     |      |

| 6   | CML-I      | Tx4p    | Transmitter non-inverted data input |      |

| 7   |            | GND     | Ground                              |      |

| 8   | LVTTL-I    | MoDSeIL | Module Select                       |      |

| 9   | LVTTL-I    | ResetL  | Module Reset                        |      |

| 10  |            | VccRx   | +3.3v Receiver Power Supply         |      |

| 11  | LVCMOS-I/O | SCL     | 2-wire Serial interface clock       |      |

| 12  | LVCMOS-I/O | SDA     | 2-wire Serial interface data        |      |

| 13  |            | GND     | Ground                              |      |

| 14  | CML-O      | RX3p    | Receiver non-inverted Data Output   |      |

| 15  | CML-O      | RX3n    | Receiver inverted Data Output       |      |

| 16  |            | GND     | Ground                              |      |

| 17  | CML-O      | Rx1p    | Receiver non-inverted Data Output   |      |

| 18  | CML-O      | Rx1n    | Receiver inverted Data Output       |      |

| 19  |            | GND     | Ground                              |      |

| 20  |            | GND     | Ground                              |      |

| 21  | CML-O      | Rx2n    | Receiver Inverted Data Output       |      |

| 22  | CML-O      | Rx2p    | Receiver Non-Inverted Data Output   |      |

| 23  |            | GND     | Ground                              |      |

| 24  | CML-O      | Rx4n    | Receiver Inverted Data Output       |      |

| 25  | CML-O      | Rx4p    | Receiver Non-Inverted Data Output   |      |

| 26  |            | GND     | Ground                              |      |

| 27  | LVTTL-O    | ModPrsL | Module Present                      |      |

| 28       | LVTTL-O | IntL     | Interrupt                                                        |   |

|----------|---------|----------|------------------------------------------------------------------|---|

| 29       | EVIIL-0 | VccTx    | +3.3v Power supply transmitter                                   |   |

| 30       |         | Vcc1     | +3.3v Power supply                                               |   |

| 31       | LVTTL-I | LPMode   | Low Power Mode                                                   |   |

| 32       | LVIIL-I | GND      | Ground                                                           |   |

| 33       | CML-I   | Tx3p     | Transmitter Non-Inverted Data Input                              |   |

| 34       | CML-I   | Tx3n     | Transmitter Inverted Data Input  Transmitter Inverted Data Input |   |

| 35       | CIVIL-I | GND      | Ground                                                           |   |

| 36       | CML-I   | Tx1p     | Transmitter Non-Inverted Data Input                              |   |

| 37       |         | •        | ·                                                                |   |

|          | CML-I   | Tx1n     | Transmitter Inverted Data Input                                  |   |

| 38       |         | GND      | Ground                                                           |   |

| 39       | 0.41.1  | GND      | Ground                                                           |   |

| 40       | CML-I   | Tx6n     | Transmitter Inverted Data Input                                  |   |

| 41       | CML-I   | Тх6р     | Transmitter Non-Inverted Data Input                              |   |

| 42       |         | GND      | Ground                                                           |   |

| 43       | CML-I   | Tx8n     | Transmitter Inverted Data Input                                  |   |

| 44       | CML-I   | Тх8р     | Transmitter Non-Inverted Data Input                              |   |

| 45       |         | GND      | Ground                                                           |   |

| 46       |         | Reserved | For future use                                                   |   |

| 47       |         | VS1      | Module Vendor Specific 1                                         |   |

| 48       |         | VccRx1   | 3.3V Power Supply                                                |   |

| 49       |         | VS2      | Module Vendor Specific 2                                         |   |

| 50       |         | VS3      | Module Vendor Specific 3                                         |   |

| 51       |         | GND      | Ground                                                           |   |

| 52       | CML-O   | Rx7p-    | Receiver Non-Inverted Data Output                                |   |

| 53       | CML-O   | Rx7n     | Receiver Inverted Data Output                                    |   |

| 54       |         | GND      | Ground                                                           |   |

| 55       | CML-O   | Rx5p-    | Receiver Non-Inverted Data Output                                |   |

| 56       | CML-O   | Rx5n     | Receiver Inverted Data Output                                    |   |

| 57       |         | GND      | Ground                                                           |   |

| 58       |         | GND      | Ground                                                           |   |

| 59       | CML-O   | Rx6n-    | Receiver Inverted Data Output                                    |   |

| 60       | CML-O   | Rx6p     | Receiver Non-Inverted Data Output                                |   |

| 61       |         | GND      | Ground                                                           |   |

| 62       | CML-O   | Rx8n     | Receiver Inverted Data Output                                    |   |

| 63       | CML-O   | Rx8p     | Receiver Non-Inverted Data Output                                |   |

| 64       |         | GND      | Ground                                                           |   |

| 65       |         | NC       | No connect                                                       |   |

| 66       |         | Reserved | For future use                                                   |   |

| 67       |         | VccTx1   | 3.3V Power Supply                                                |   |

| 68       |         | Vcc2     | 3.3V Power Supply                                                |   |

| 69       |         | Reserved | For Future Use                                                   |   |

| 70       |         | GND      | Ground                                                           | 1 |

| 71       | CML-I   | Тх7р     | Transmitter Non-Inverted Data Input                              |   |

| 72       | CML-I   | Tx7n     | Transmitter Inverted Data Input                                  | 1 |

| 73       | 5       | GND      | Ground                                                           | 1 |

| 74       | CML-I   | Тх5р     | Transmitter Non-Inverted Data Input                              | † |

| 75       | CML-I   | Tx5n     | Transmitter Inverted Data Input                                  |   |

| 75<br>76 | CIVIL   | GND      | Ground                                                           | + |

| 70       |         | טוזט     | Ground                                                           | 1 |

- QSFP-DD uses common ground (GND) for all signals and supply (power). All are common within the QSFP-DD module and all module voltages are referenced to this potential unless otherwise noted. Connect these directly tothe host board signal-common ground plane.

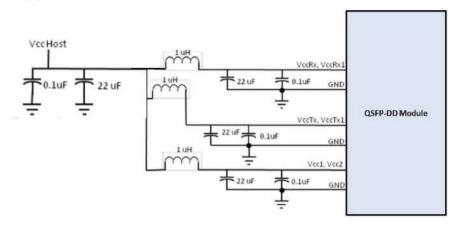

- 2. VccRx, RccRx1, Vcc1, Vcc2, VccTx and VccTx1 shall be applied concurrently. Requirements defined for the hostside of the Host Card Edge Connector. VccRx, VccRx1, Vccl, Vcc2, VccTx and VccTx1 may be internally connected within the module in any combination. The corrector Vcc pins are each rated for a maximum current of1000mA.

- 3. All Vendor Specific, Reserved, No connect and ePPS (if not used) pins may be terminated with 50 Ohms to ground on the host. Pad 65 (No Connect) shall be left unconnected within the module. Vendor specific and Reserved pads shall have an impedance to GND that is greater than 10 kOhms and less than 100pF.

- 4. Plug Sequence specifies the mating sequence of the host connector and module. The sequence is 1A, 2A, 3A,1B, 2B, 3B. (see Figure 2 for pad locations) Contact sequence A will make, then break contact with additional QSFP-DD pads. Sequence 1A, 1B will then occur simultaneously, followed by 2A, 2B, followed by 3A, 3B.

## **Recommended Power Supply Filter**

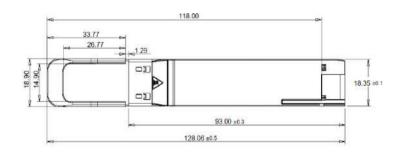

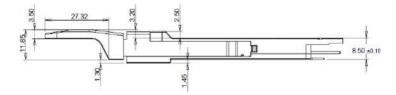

#### **Dimensions**

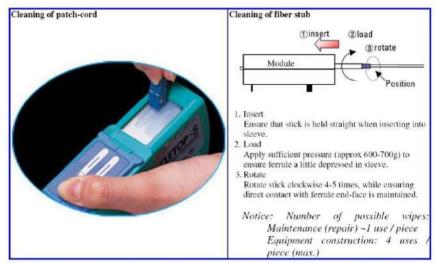

#### **Optical Receptacle Cleaning Recommendations:**

All fiber stubs inside the receptacle portions were cleaned before shipment. In the event of contamination of the optical ports, the recommended cleaning process is the use of forced nitrogen. If contamination is thought to have remained, the optical ports can be cleaned using a NTT international Cletop® stick type and HFE7100 cleaning fluid. Before the mating of patch-cord, the fiber end should be cleaned up by using Cletop® cleaning cassette.

Note: The pictures were extracted from NTT-ME website. And the Cletop® is a trademark registered by NTT-ME

**Ordering Information**

| Model Number  | Part Number     | Reach | Wavelength | Temperature |

|---------------|-----------------|-------|------------|-------------|

| AQSFP-DD-DR4+ | OPDY-S02-13-CBS | 2km   | 1310nm     | 0°Cto 70°C  |

Note: All information contained in this document is subject to change without notice.

This document is ABTPL Public Information. ABTPL reserves the right to alter, update, and otherwise change the information contained in the document from time to time. www.alphabridge.tech